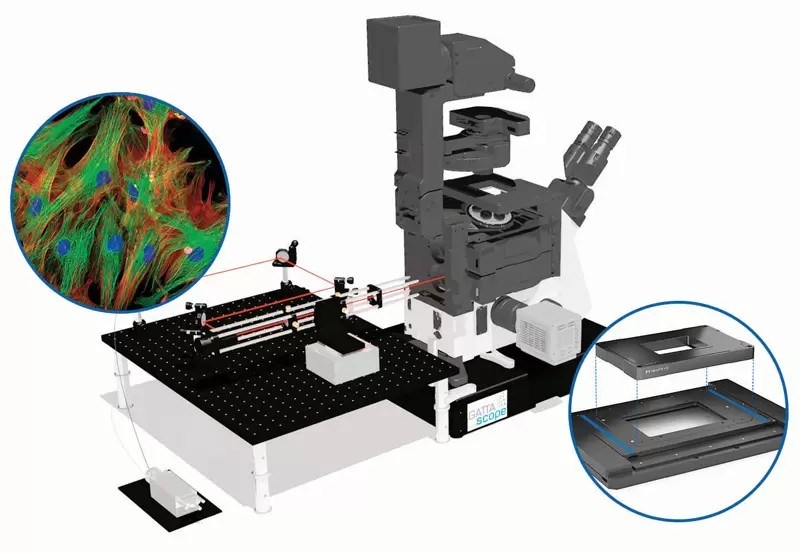

Trong các lĩnh vực khoa học đời sống, phân tích hóa dược hay khoa học vật liệu hiện đại, độ phân giải quang học và nội dung thông tin của các phương pháp hiển vi cổ điển đã không còn đủ đáp ứng. Để có được thông tin toàn diện nhất về một mẫu vật, các hệ thống kính hiển vi độ phân giải cao. Do việc định vị mẫu năng động và chính xác cực cao là yếu tố không thể thiếu trong hầu hết các lĩnh vực ứng dụng, các bàn quét dựa trên piezo là một giải pháp tối ưu.

Laser là những công cụ đa năng với phạm vi ứng dụng rộng lớn. Ví dụ, trong xử lý vật liệu, chúng ngày nay trở nên không thể thiếu, tương tự như trong công nghệ y tế hoặc trong nghiên cứu vật liệu và môi trường. Ở mọi nơi, nguyên lý đều giống nhau: Các gương lật/nghiêng (tip/tilt mirrors) đảm bảo việc điều hướng chính xác chùm tia laser

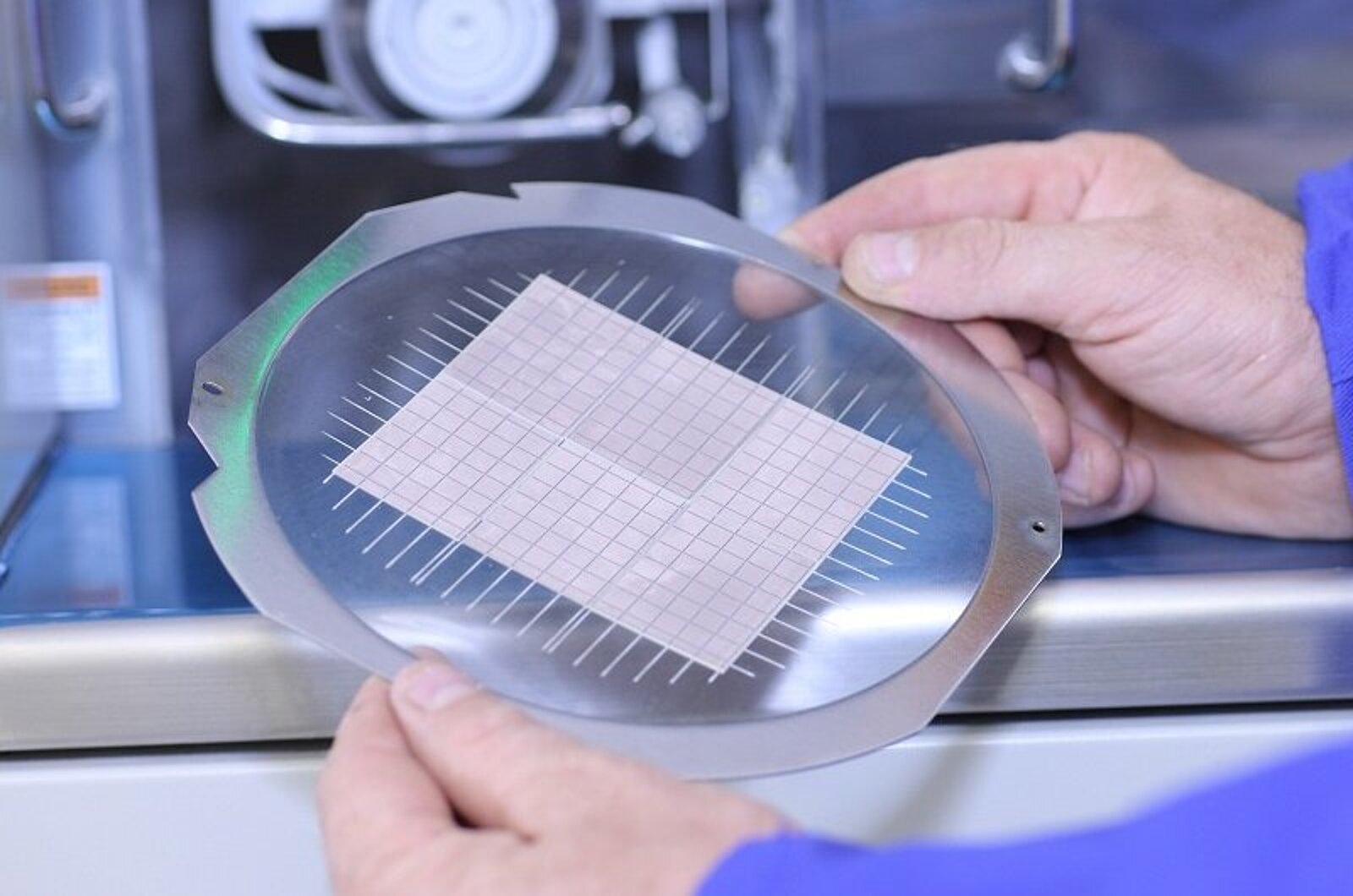

Trong kỷ nguyên của AI và IoT, tấm Wafer bán dẫn được ví như "mảnh đất đắt nhất thế giới". Tuy nhiên, đằng sau những con chip kích thước nanomet (nm) là một quy trình sản xuất cực kỳ tốn kém và nhạy cảm. Chỉ một rung động nhỏ hay sai số vị trí ở cấp độ nguyên tử cũng có thể biến một tấm Wafer trị giá hàng chục nghìn USD thành phế phẩm.

Trong kỷ nguyên của AI và IoT, tấm Wafer bán dẫn được ví như "mảnh đất đắt nhất thế giới". Tuy nhiên, đằng sau những con chip kích thước nanomet (nm) là một quy trình sản xuất cực kỳ tốn kém và nhạy cảm. Chỉ một rung động nhỏ hay sai số vị trí ở cấp độ nguyên tử cũng có thể biến một tấm Wafer trị giá hàng chục nghìn USD thành phế phẩm.

Đĩa Wafer - Đĩa bán dẫn

Trước khi đi sâu vào giải pháp, chúng ta cần hiểu rõ "kẻ thù" của chi phí trong nhà máy Fab (Fabrication Plant).

Quy trình sản xuất một tấm Wafer silicon 300mm (12 inch) tiên tiến có thể tiêu tốn hàng nghìn bước xử lý trong nhiều tháng.

Giá trị hàng lỗi (Scrap cost): Một tấm Wafer thành phẩm chứa hàng ngàn die (con chip). Nếu xảy ra lỗi lệch lớp (overlay error) trong quá trình quang khắc, toàn bộ tấm Wafer đó phải bị loại bỏ. Thiệt hại không chỉ là vật liệu silicon, mà là chi phí vận hành máy móc đắt đỏ đã bỏ ra trước đó.

Áp lực về "Yield" (Tỷ lệ thành phẩm): Trong ngành bán dẫn, Yield là vua. Tăng 1% tỷ lệ thành phẩm có thể mang lại hàng triệu USD lợi nhuận ròng. Ngược lại, thiết bị rung lắc hoặc định vị sai sẽ kéo Yield xuống đáy.

Thời gian là vàng: Các máy móc như máy quang khắc (Lithography scanner) hay máy đo lường (Metrology) có giá từ hàng chục đến hàng trăm triệu USD. Mỗi giây máy ngừng hoạt động hoặc phải quét lại mẫu (re-scan) do hình ảnh mờ nhòe đều là sự lãng phí khổng lồ.

Đây chính là lúc công nghệ của Physik Instrumente (PI) bước vào cuộc chơi.

PI không chỉ cung cấp thiết bị chuyển động, họ cung cấp sự đảm bảo về độ chính xác. Dưới đây là cách PI can thiệp vào các khâu "nhạy cảm" nhất để giảm thiểu rủi ro và chi phí.

Quang khắc là bước đắt đỏ và quan trọng nhất, nơi các mẫu mạch điện được in lên Wafer. Khi các node công nghệ xuống dưới 7nm hoặc 3nm, yêu cầu về độ chính xác chồng lớp (Overlay accuracy) là cực hạn.

Vấn đề: Chỉ cần một rung động từ môi trường hoặc sự giãn nở nhiệt nhỏ cũng làm lệch chùm tia, gây ra lỗi ngắn mạch trên chip.

Giải pháp PI: PI cung cấp các hệ thống Piezo Actuators và bàn dịch chuyển Nanopositioning tích hợp ngay trong ống kính và bệ đỡ Wafer.

Khả năng: Phản hồi trong tích tắc (mili-giây) để bù trừ các rung động vi mô, giữ cho Wafer và mặt nạ (mask) luôn đồng bộ tuyệt đối.

Lợi ích kinh tế: Giảm thiểu tối đa lỗi in (patterning defects), từ đó giảm tỷ lệ Wafer bị loại bỏ ngay từ bước đầu tiên.

Sau mỗi lớp in, Wafer phải được kiểm tra lỗi. Đây là nút thắt cổ chai (bottleneck) của dây chuyền vì quá trình quét tốn nhiều thời gian.

Vấn đề: Để phát hiện lỗi kích thước nanomet, camera độ phân giải cao phải quét bề mặt Wafer liên tục. Các hệ thống chuyển động dùng bi (mechanical bearings) thường có ma sát, gây ra rung động (velocity ripple) làm nhòe ảnh, buộc máy phải quét chậm lại hoặc quét lại.

Giải pháp PI: Sử dụng Bàn dịch chuyển đệm khí (Air Bearing Stages) – Dòng sản phẩm chủ lực của PI cho mảng bán dẫn.

Công nghệ: Bàn di chuyển trượt trên một lớp khí nén mỏng, hoàn toàn không có ma sát cơ học, không mài mòn, không sinh bụi.

Hiệu suất: Đảm bảo độ phẳng tuyệt đối và tốc độ quét (scanning velocity) cực kỳ ổn định.

Lợi ích kinh tế: Tăng tốc độ kiểm tra (Throughput) lên gấp nhiều lần mà vẫn đảm bảo ảnh sắc nét. Máy chạy nhanh hơn đồng nghĩa với chi phí khấu hao trên mỗi tấm Wafer thấp hơn.

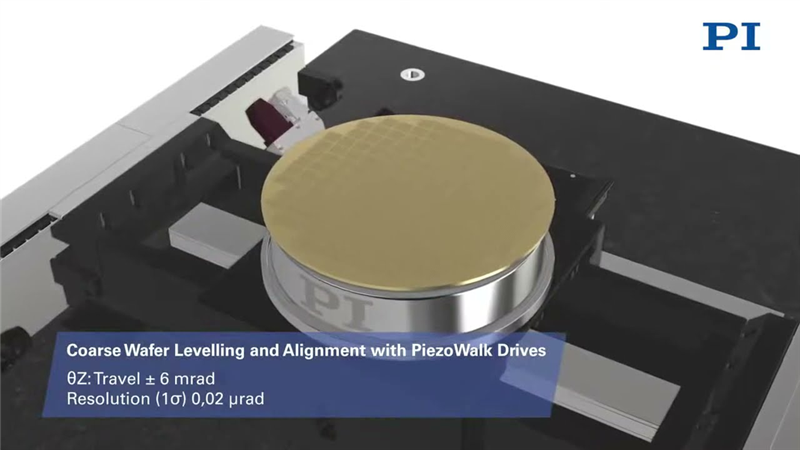

Khi Wafer hoàn thiện được cắt thành từng chip nhỏ (die), công nghệ đóng gói 3D (xếp chồng chip) đòi hỏi sự căn chỉnh chính xác không kém gì quang khắc.

Vấn đề: Tia laser cắt rãnh (Laser dicing) cần hội tụ chính xác vào các "con phố" (street) siêu nhỏ giữa các chip. Lệch tia sẽ cắt hỏng vào vùng mạch điện (active area).

Giải pháp PI: Hệ thống Robot 6 trục Hexapod và Piezo Focus Stages.

Công nghệ: Hexapod giúp căn chỉnh Wafer theo 6 bậc tự do (bao gồm cả độ nghiêng), đảm bảo bề mặt Wafer luôn vuông góc tuyệt đối với tia laser. Piezo Stage di chuyển thấu kính lên xuống cực nhanh để giữ tiêu cự (autofocus) ngay cả khi bề mặt Wafer không bằng phẳng.

Lợi ích kinh tế: Tối đa hóa số lượng chip thu được trên mỗi tấm Wafer (Chips per Wafer), đặc biệt quan trọng với các loại chip AI/GPU đắt tiền.

Nhiều nhà sản xuất ban đầu e ngại chi phí đầu tư cho thiết bị cao cấp của Đức. Tuy nhiên, trong bài toán kinh tế tổng thể của nhà máy bán dẫn (Total Cost of Ownership), PI lại là phương án tiết kiệm nhất.

Độ Tin Cậy & Uptime (Thời gian hoạt động): Công nghệ Piezo gốm của PI (do PI tự sản xuất vật liệu PICMA®) đã được chứng minh có tuổi thọ lên tới 100 tỷ chu kỳ hoạt động mà không hỏng hóc. Điều này giúp giảm chi phí bảo trì và thời gian chết của dây chuyền (downtime cost).

Sạch Tuyệt Đối: Các giải pháp Air Bearing và Piezo của PI không sinh ra bụi ma sát, giảm tải cho hệ thống lọc khí phòng sạch (Cleanroom) và giảm nguy cơ bụi rơi vào làm hỏng chip.

Khả Năng Tùy Biến (Customization): PI thiết kế hệ thống vừa vặn với quy trình cụ thể của khách hàng, giúp tối ưu hóa không gian máy và hiệu năng xử lý.

Trong cuộc đua bán dẫn khốc liệt, nơi chi phí sản xuất một tấm Wafer 3nm đang tăng phi mã, không có chỗ cho sai sót. Việc tích hợp các giải pháp chuyển động chính xác của Physik Instrumente (PI) vào dây chuyền sản xuất – từ quang khắc, đo lường đến đóng gói – không chỉ là vấn đề kỹ thuật, mà là chiến lược kinh tế sống còn.

PI giúp các nhà sản xuất biến rủi ro thành lợi nhuận bằng cách: Tăng Yield, Tăng tốc độ kiểm tra (Throughput) và Giảm thiểu thời gian chết.

Cập nhật thêm kiến thức về quản lý chất lượng qua chuyên mục đào tạo tại: https://v-proud.vn/vi/danh-muc/tin-dao-tao

Đọc thêm:

(84) 896 555 247